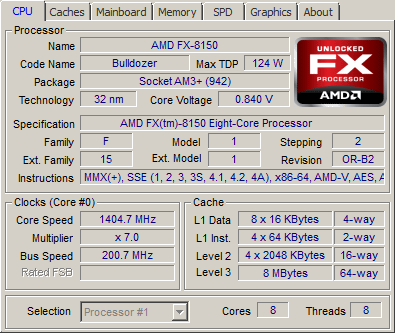

CPU is unlocked for overclocking.

AMD FX-8150 processor review. Buy on Amazon Buy on Ebay. FX-8150 processor released by AMD release date: October 2011.

Note that higher-end graphic cards have more benefit from faster processor, and its vice verse for lower-end graphic cards.Chainlink Review: LINKing the World to Blockchain. 2021 AMD FX-8350 XMRig RandomX Hashrate Benchmark AMD FX-8350 Monero RandomX Hashrate Benchmark. Maximum CPU clock speed - 4.2 GHz.Gaming TestsAnd finally some gaming benchmarks, the favorite review page for gamers. Five popular titles are chosen in effort represent every game genre. Metro 2033 for FPS gamers, Batman and Mafia II for adventure and 3rd person style gamers, Formfor racers and Dawn of War 2 for those who like to play RTS genre games.

Benchmark score Compare AMD FX-8150 Eight-Core performance to most popular processors CPU Benchmark AMD FX-8150 Eight-Core Intel Pentium G4560 Intel i3 8100 AMD RyIntel i7 9700K Intel i9 9900K AMD Ryzen Threadripper 2950X Intel Core i9- 9980XE 0 10k 20k. 8 (in 4 physical modules) Created with Highcharts 7.2.0. This optimises the performance in light multi-threaded applications and demanding low-threaded applications.As for in game quality settings, a single most commonly used resolution is chosen in combination with golden middle video quality settings. Anti aliasing on all games is turned off, as this only puts additional workload on graphic cards, and with it turned off it enables more breathing space for graphic card to show any performance increase when paired with stronger type of processor.

In fact, the firm has been working for several years on a brand-new breed of PC processors based on a fresh microarchitecture, code-named “Bulldozer,” that aims to restore some competitive balance. The introduction of Sandy Bridge processors at the beginning of this year put Intel firmly in the lead in terms of overall performance, power efficiency, and the value proposition offered to consumers.Being the perennial number-two CPU maker in such a competitive context can’t be easy, but AMD hasn’t taken the challenge lightly. Since then, Intel has turned over new manufacturing technologies followed by extensively revised CPU architectures in relentless succession. The sound of Intel’s ongoing CPU development cycle has been constantly in the backdrop for its biggest competitor, AMD, ever since the world’s largest chipmaker set an aggressive cadence for itself more than five years ago. With the following specifications: AMD FX-8150 3.61Ghz Eight-Core Virtual.

The Bulldozer module is sort of a mid-point between those two familiar arrangements. To date, we’ve seen x86-compatible CPU cores capable of tracking and executing two threads via a feature known as simultaneous multithreading (SMT), better known by its Intel marketing name, Hyper-Threading, and we’ve had a number of chips with multiple cores onboard in a chip-level multiprocessor (CMP) configuration, tracing back to the original Athlon 64 X2. The first of those is a dual-core “module” as a fundamental building block. Bulldozer draws on that tradition in various ways, but it is a novel, clean-sheet design intended to take AMD processors into their next era.To that end, Bulldozer introduces some unorthodox concepts into the PC processor space.

That voltage squared term is, obviously, the single biggest factor in the power equation, so a design capable of keeping voltage in check could make some sense for today’s power-constrained world.We don’t know precisely how aggressively AMD has pursued the speed-demon approach. Chip power consumption has three main determinants: clock speed, the number of transistors flipping, and the square of the voltage. The rationale, if we understand Butler correctly, is that a design with a relatively low number of gates flipping at each pipeline stage may require less voltage to operate at a given frequency. Yet Chief Architect Mike Butler told us the engineering team’s goal with Bulldozer was to “hold the line” on instructions per clock (presumably at about the same rate as the Phenom II) and to “aggressively pursue higher frequencies.” Speed demons have typically reduced the amount of work done at each stage of the pipeline in order to simplify logic and thus enable higher operating frequencies, but this approach can also theoretically help manage power consumption. The Pentium 4 “Netburst” microarchitecture—particularly in its troubled “Prescott” incarnation—gave frequency-optimized designs a reputation for high power draw and iffy performance. The idea is to save space on the silicon die by pooling resources where possible while still offering “robust” performance on both threads, with fewer of the performance hazards created by SMT or Hyper-Threading.At the same time, Bulldozer resurrects a concept that’s fallen out of favor in PC processors in recent years: it’s a “speed demon,” optimized for higher clock frequencies rather than maximum instruction throughput in each clock cycle.

With two integer cores featuring relatively long pipelines to keep fed, the front-end hardware must be very effective at its job in order for the whole chip to function efficiently.The decode units dispatch ops, or decoded instructions, to the two integer cores on an interleaved, every-other-cycle basis. Source: AMD.The sharing in a Bulldozer module starts with the front end, where the branch prediction, instruction fetch, and decode units track two threads and service both cores. I expect we’ll learn more about Bulldozer’s inner workings as time passes.Block diagram of a Bulldozer module. Our sense is that it’s somewhere between the 12-14 stages of contemporary Core- and Phenom-branded chips and the astounding 31 stages in Prescott. We’ve been writing about these things for over a decade, and an outright refusal to disclose pipeline depth in a major x86 processor is very rare. This behavior seems unusually guarded.

If only one thread is active, these resources are fully used by that single thread.Another major shared resource in the Bulldozer module is the floating-point unit, which has been spun off into a co-processor arrangement in which both integer cores act as clients. Both the prefetchers and the L2 cache into which they pull data are shared between the two cores in a module, assuming both cores have active threads. Memory access latencies should be further reduced by the use of multiple data prefetchers that operate according to different rules in order to keep the caches populated with, hopefully, the appropriate data for the cores’ upcoming work. Among other things, the memory pipeline can speculatively move loads ahead of stores if doing so won’t cause a problem, a capability Intel has called memory disambiguation. However, instruction scheduling is more flexible, and beyond the obvious increase in integer core counts, Bulldozer seeks to make things up in other ways.One of those ways is a vastly reworked memory subsystem that looks very different from those in prior AMD chips. Thus, individual Bulldozer cores have fewer execution resources than those in the preceding Deneb/Thuban architecture.

The result should be much higher peak computational throughput on data-parallel workloads.However, the path to that destination will have a few twists and turns. AVX increases parallelism by extending the width of vectors from 128 to 256 bits, and supporting those wider datatypes requires the broad reworking of the processor’s execution engine. The common thread is the advent of the follow-on to SSE, the extended instruction set known as Advanced Vector Extensions, or AVX. Yes, that means integer SIMD goodness happens in the FPU, as well as floating-point math.The fact that both Bulldozer and Sandy Bridge, two substantially new x86 microarchitectures, have hit the streets within the same calendar year isn’t entirely coincidental. The scheduler can track two threads, of course, and the execution units include dual FMAC units capable of processing 128-bit vectors in a single clock cycle, along with dual 128-bit integer units (marked as “MMX” in the diagram above). For now, though, Bulldozer’s FPU is quite formidable in its own right.

Where Bulldozer moves beyond Sandy Bridge, though, is with those two 128-bit FMAC pipes—and there, we get into disputed territory.The dispute is over the FMAC instruction, which is the key to unlocking AVX’s peak potential. It also includes support for AMD’s own XOP extensions, a surviving bit of SSE5 with more of a focus on integer datatypes. So Bulldozer catches up with Sandy Bridge on nearly every front, adding support for SSE 4.1 and 4.2 and most of AVX, including the AES instructions for accelerating encryption. As that change was happening, Intel apparently was modifying its own course, as well.

Sandy Bridge doesn’t, and the upcoming Ivy Bridge won’t, either. These virtues have made FMAC very popular in other chips, including DirectX 11-class GPUs.Bulldozer is the first x86 CPU to support FMAC. The FMAC form of this instruction has a further precision advantage because the results of one operation are fed directly into the other, at the chip’s full internal precision, without being stored. Doing both operations at once has a performance benefit, obviously—the processor is executing two floating-point operations (FLOPS) per clock cycle. Instructions that combine a multiply and an add together tend to map well to multimedia workloads, and they have been a staple of GPU shader cores for quite some.

Bulldozer can theoretically match Sandy’s peak throughput, either by processing dual 128-bit FMACs or a single 256-bit FMAC per cycle, but it can’t match Sandy without FMAC.

0 kommentar(er)

0 kommentar(er)